- 您现在的位置:买卖IC网 > Sheet目录3840 > PIC18F6410-I/PT (Microchip Technology)IC PIC MCU FLASH 8KX16 64TQFP

2010-2012 Microchip Technology Inc.

DS39977F-page 187

PIC18F66K80 FAMILY

11.6

PORTE, TRISE and

LATE Registers

PORTE is a seven-bit-wide, bidirectional port. The

corresponding Data Direction and Output Latch registers

are TRISE and LATE.

All pins on PORTE are implemented with Schmitt

Trigger input buffers. Each pin is individually

configurable as an input or output.

Each of the PORTE pins has a weak internal pull-up. A

single control bit can turn off all the pull-ups. This is

performed by clearing bit, REPU (PADCFG1<6>). The

weak pull-up is automatically turned off when the port

pin is configured as an output. The pull-ups are

disabled on any device Reset.

PORTE is also multiplexed with the Parallel Slave Port

address lines. RE1 and RE0 are multiplexed with the

Parallel Slave Port (PSP) control signals, WR and RD.

EXAMPLE 11-5:

INITIALIZING PORTE

Note:

PORTE is unavailable on 28-pin devices.

Note:

These pins are configured as digital inputs

on any device Reset.

CLRF

PORTE

; Initialize PORTE by

; clearing output

; data latches

CLRF

LATE

; Alternate method

; to clear output

; data latches

MOVLW

03h

; Value used to

; initialize data

; direction

MOVWF

TRISE

; Set RE<1:0> as inputs

; RE<7:2> as outputs

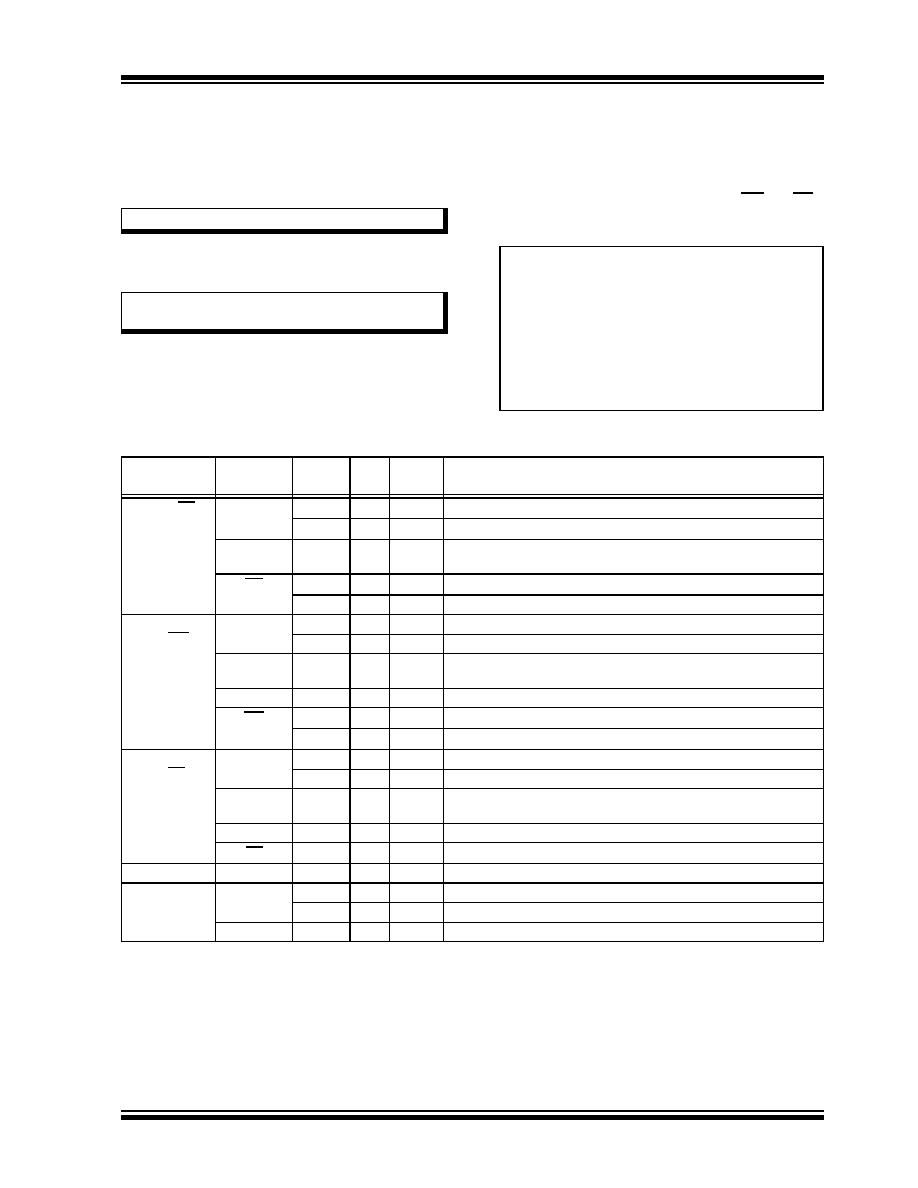

TABLE 11-9:

PORTE FUNCTIONS

Pin Name

Function

TRIS

Setting

I/O

I/O Type

Description

RE0/AN5/RD

RE0

0

O

DIG

LATE<0> data output.

1

I

ST

PORTE<0> data input.

AN5

1

I

ANA

A/D Input Channel 5. Default input configuration on POR; does not

affect digital output.

RD

x

O

DIG

Parallel Slave Port read strobe pin.

x

I

ST

Parallel Slave Port read pin.

RE1/AN6/

C1OUT/WR

RE1

0

O

DIG

LATE<1> data output.

1

I

ST

PORTE<1> data input.

AN6

1

I

ANA

A/D Input Channel 5. Default input configuration on POR; does not

affect digital output.

C1OUT

0

O

DIG

Comparator 1 output; takes priority over port data.

WR

x

O

DIG

Parallel Slave Port write strobe pin.

x

I

ST

Parallel Slave Port write pin.

RE2/AN7/

C2OUT/CS

RE2

0

O

DIG

LATE<2> data output.

1

I

ST

PORTE<2> data input.

AN7

1

I

ANA

A/D Input Channel 7. Default input configuration on POR; does not

affect digital output.

C2OUT

0

O

DIG

Comparator 2 output; takes priority over port data.

CS

x

I

ST

Parallel Slave Port chip select.

RE3

1

I

ST

PORT<3> data input.

RE4/CANRX

RE4(1)

0

O

DIG

LATE<4> data output.

1

I

ST

PORTE<4> data input.

CANRX(1,2)

1

I

ST

CAN bus RX.

Legend:

O = Output, I = Input, ANA = Analog Signal, DIG = CMOS Output, ST = Schmitt Trigger Buffer Input,

x

= Don’t care (TRIS bit does not affect port direction or is overridden for this option)

Note

1:

These bits are unavailable for 40 and 44-pin devices (PIC18F4XK0).

2:

This is the alternate pin assignment for CANRX and CANTX on 64-pin devices (PIC18F6XK80) when the CANMX

Configuration bit is cleared.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

200346-2

CONN HOUSING RECEPT 20POS BLACK

PIC16F84A-20/P

IC MCU FLASH 1KX14 EE 18DIP

200838-2

CONN HOUSING RECEPT 34POS BLACK

PIC18LF2420-I/SO

IC MCU FLASH 8KX16 28SOIC

5172625-3

CONN RCPT HSNG 24POS BLUE PNL MT

202758-1

CONN HOUSING PLUG 6POS BLACK

TS80C31X2-VIC

IC MCU 8BIT 40/30MHZ 44-PQFP

TS80C31X2-MCC

IC MCU 8BIT 40/20MHZ 44-PQFP

相关代理商/技术参数

PIC18F6410-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F6410 TQFP64

PIC18F6410T-I/PT

功能描述:8位微控制器 -MCU 16kBF 768RM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F6490-E/PT

功能描述:8位微控制器 -MCU 16kBF 768RM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F6490-I/PT

功能描述:8位微控制器 -MCU 16kBF 768RM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F6490-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F6490 TQFP64

PIC18F6490-I/PT

制造商:Microchip Technology Inc 功能描述:8 BIT MICROCONTROLLER CLOCK SPEED:40MHZ

PIC18F6490T-I/PT

功能描述:8位微控制器 -MCU 16kBF 768RM 68I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F6493-I/PT

功能描述:8位微控制器 -MCU 128 Segmnt LCD DRVR 12B ADC 16KB 768BRAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT